# Infineon<sup>®</sup> Power LED Driver

# TLD5085EJ 1.8A DC/DC Step-Down Converter

# Datasheet

Rev. 1.1, 2009-12-16

# Automotive Power

#### 1.8A DC/DC Step-Down Converter

#### TLD5085EJ

#### 1 Overview

- Wide Input Voltage Range from 4.75V to 45V

- Constant Current or Constant Voltage Regulation

- Drives LEDs in Buck Topology

- Very low shutdown current consumption (typ. 0.1µA)

- 370 kHz switching frequency

- PWM Dimming

- Integrated power-switch (output current up to 1.8A)

- Internal Soft-Start function

- ± 2% output current tolerance (± 4% for full load current range)

- Small thermally enhanced exposed heatslug package

- Over Temperature Shutdown

- AEC Qualified

- Green Product (RoHS Compliant)

PG-DSO-8 (e-Pad)

#### Description

The TLD5085EJ is a smart LED buck converter with an integrated power-switch, capable of driving up to 1.8A load current with excellent line and load regulation. The main function of this device is to step-down the input voltage and regulating a constant LED current. The constant current regulation is especially beneficial for LED color accuracy and longer lifetime. The TLD5085EJ also has a PWM input which can be used for LED dimming. The switching frequency of 370kHz allows to use small and inexpensive passive components. An Enable function is implemented to reduce the shut-down current consumption to typ.  $0.1\mu$ A. This IC is suited for use in the harsh automotive environments and provides protection functions such as current limitation and overtemperature shutdown. The integrated soft-start feature avoids a current and voltage overshot at the output during start-up of the device.

#### Applications

- Automotive Lighting (Reading Light, Dome Light, Dashboard Backlighting)

- High Power LED Applications

- Constant Current and Voltage Source

| Туре      | Package          | Marking |

|-----------|------------------|---------|

| TLD5085EJ | PG-DSO-8 (e-Pad) | TLD5085 |

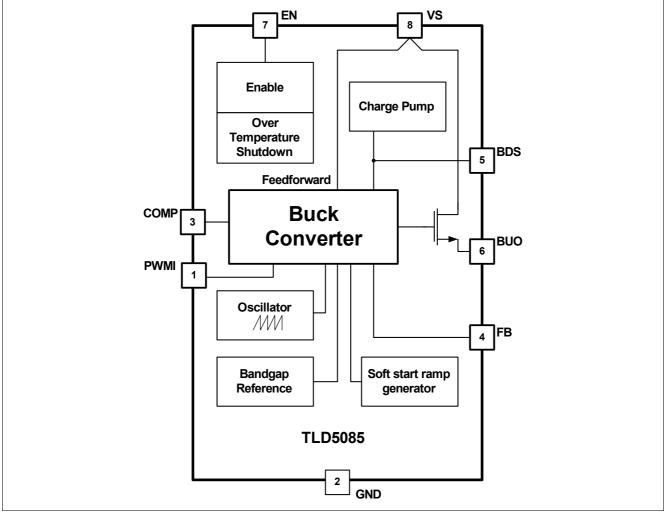

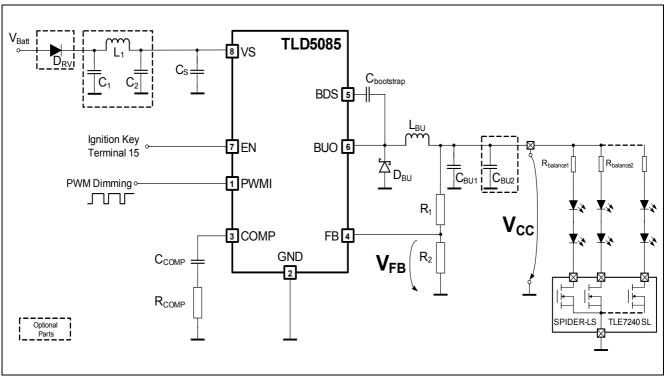

**Block Diagram**

# 2 Block Diagram

Figure 1 Block Diagram

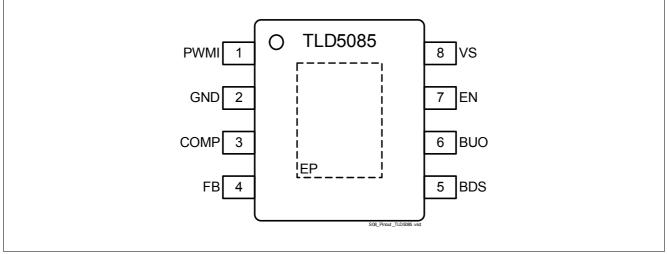

#### **Pin Configuration**

# 3 Pin Configuration

## 3.1 Pin Assignment

Figure 2 Pin Configuration

### 3.2 Pin Definitions and Functions

| Pin | Symbol | Function                                                                                                                                                                                                                       |

|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | PWMI   | <b>PWM Input for;</b><br>Provides LED dimming option. If not used connect to VS.                                                                                                                                               |

| 2   | GND    | Ground;<br>Connect to system ground.                                                                                                                                                                                           |

| 3   | COMP   | <b>Compensation Input;</b><br>Frequency compensation for regulation loop stability.<br>Connect R and C network to pin for stability.                                                                                           |

| 4   | FB     | <b>Feedback Input;</b><br>Connect a defined power resistor (RFB=0.6V/ILED) to get the needed LED output current.<br>For adjustable output voltages connect this pin via a voltage divider in parallel to the output capacitor. |

| 5   | BDS    | Buck Driver Supply Input;<br>Connect the bootstrap capacitor between this pin and pin BUO.                                                                                                                                     |

| 6   | BUO    | <b>Buck Switch Output;</b><br>Source of the integrated power-switch. Connect directly to the cathode of external freewheeling diode and the buck circuit inductance.                                                           |

| 7   | EN     | <b>Enable Input;</b><br>Apply logic high signal to enable the device. A pull down resistor is integrated.                                                                                                                      |

| 8   | VS     | Supply Voltage Input;<br>Connect to supply voltage source.                                                                                                                                                                     |

| EP  |        | Exposed Pad;<br>Connect to heatsink area and GND by low inductance wiring.                                                                                                                                                     |

# 4 General Product Characteristics

#### 4.1 Absolute Maximum Ratings

#### Absolute Maximum Ratings <sup>1)</sup>

$T_i$  = -40 °C to +150 °C; all voltages with respect to ground (unless otherwise specified)

| Pos.     | Parameter                                      | Symbol                | Lim  | nit Values                | Unit | Conditions        |  |

|----------|------------------------------------------------|-----------------------|------|---------------------------|------|-------------------|--|

|          |                                                |                       | Min. | Max.                      |      |                   |  |

| Voltage  | S                                              | I                     | 1    |                           |      |                   |  |

| 4.1.1    | PWMI (Pin1)<br>PWM Input                       | $V_{PWMI}$            | -0.3 | 45                        | V    | -                 |  |

| 4.1.2    | COMP (Pin 3)                                   | V <sub>COMP</sub>     | -0.3 | 5.5                       | V    | -                 |  |

| 4.1.3    | Compensation Input                             |                       |      | 6.2                       | V    | $t < 10s^{2}$     |  |

| 4.1.4    | FB (Pin 4)<br>Feedback Input                   | $V_{FB}$              | -0.3 | 5.5                       | V    | -                 |  |

| 4.1.5    | BDS (Pin 5)<br>Buck Driver Supply Input        | nput V <sub>BDS</sub> |      | V <sub>BUO</sub><br>+ 5.5 | V    | -                 |  |

| 4.1.6    | BUO (Pin 6)<br>Buck Switch Output              | V <sub>BUO</sub>      | -2.0 | V <sub>VS</sub> + 0.3     | V    | -                 |  |

| 4.1.7    | EN (Pin 7)<br>Enable Input                     | $V_{\sf EN}$          | -40  | 45                        | V    | -                 |  |

| 4.1.8    | VS (Pin 8)<br>Supply Voltage Input             | Vs                    | -0.3 | 45                        | V    | -                 |  |

| Temper   | atures                                         |                       |      | ·                         |      | - I-              |  |

| 4.1.9    | Junction Temperature                           | $T_{i}$               | -40  | 150                       | °C   | -                 |  |

| 4.1.10   | Storage Temperature                            | T <sub>stg</sub>      | -55  | 150                       | °C   | _                 |  |

| ESD Su   | sceptibility                                   |                       | 1    | I                         |      |                   |  |

| 4.1.11   | ESD Resistivity all Pins to GND                | $V_{ESD}$             | -2   | 2                         | kV   | HBM <sup>3)</sup> |  |

| 1) Not s | ubject to production test, specified by design |                       | 1    | 1                         | 1    | <u> </u>          |  |

1) Not subject to production test, specified by design

2) Exposure to those absolute maximum ratings for extended periods of time (t > 10s) may affect device reliability

3) ESD susceptibility HBM according to EIA/JESD 22-A 114B (1.5kΩ,100pF).

Note: Stresses above the ones listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Note: Integrated protection functions are designed to prevent IC destruction under fault conditions described in the data sheet. Fault conditions are considered as "outside" normal operating range. Protection functions are not designed for continuous repetitive operation.

#### **General Product Characteristics**

#### 4.2 Functional Range

| Pos.  | Parameter                   | Symbol                     | Limit Values |              | Limit Values |                  | Limit Values |  | Limit Values U |  | Unit | Conditions |  |

|-------|-----------------------------|----------------------------|--------------|--------------|--------------|------------------|--------------|--|----------------|--|------|------------|--|

|       |                             |                            | Min.         | Max.         |              |                  |              |  |                |  |      |            |  |

| 4.2.1 | Supply Voltage              | Vs                         | 4.75         | 45           | V            | -                |              |  |                |  |      |            |  |

| 4.2.2 | Output Voltage adjust range | e $V_{\rm CC}$ 0.60 16 V s |              | see Figure 5 |              |                  |              |  |                |  |      |            |  |

| 4.2.3 | External buck inductor      | $L_{\rm BU}$               | 18           | 56           | μH           | see Figure 5 and |              |  |                |  |      |            |  |

| 4.2.4 | External buck capacitor     | $C_{\rm BU1}$              | 33           | 120          | μF           | Figure 6         |              |  |                |  |      |            |  |

| 4.2.5 | External buck capacitor ESR | ESR <sub>BU1</sub>         | -            | 0.3          | Ω            | - <sup>1)</sup>  |              |  |                |  |      |            |  |

| 4.2.6 | Junction Temperature        | Tj                         | -40          | 150          | °C           | -                |              |  |                |  |      |            |  |

1) See section ""Application Information" on Page 11" for loop compensation requirements.

Note: Within the functional range the IC operates as described in the circuit description. The electrical characteristics are specified within the conditions given in the related electrical characteristics table.

#### 4.3 Thermal Resistance

Note: This thermal data was generated in accordance with JEDEC JESD51 standards. For more information, go to www.jedec.org.

| Pos.  | Parameter                  | Symbol            | nbol Limit Values |      |      | Limit Values |       | Limit Value |  | Limit Values |  | Unit | Conditions |

|-------|----------------------------|-------------------|-------------------|------|------|--------------|-------|-------------|--|--------------|--|------|------------|

|       |                            |                   | Min.              | Тур. | Max. |              |       |             |  |              |  |      |            |

| 4.3.1 | Junction to Case           | $R_{thJC}$        | -                 | -    | 10   | K/W          | 1) 2) |             |  |              |  |      |            |

| 4.3.2 | Junction to Ambient (2s2p) | R <sub>thJA</sub> | -                 | 42   | -    | K/W          | 1) 3) |             |  |              |  |      |            |

1) Not subject to production test, specified by design.

Specified R<sub>thJC</sub> value is simulated at natural convection on a cold plate setup (all pins and the exposed pad are fixed to ambient temperature). Ta=25°C, power-switch is dissipating 1W.

3) Specified RthJA value is according to Jedec JESD51-2,-5,-7 at natural convection on FR4 2s2p board; The Product (Chip+Package) was simulated on a 76.2 x 114.3 x 1.5 mm board with 2 inner copper layers (2 x 70µm Cu, 2 x 35µm Cu). According to JESD51-5 a thermal via array under the exposed pad contacted the first inner copper layer. Ta=25°C, powerswitch is dissipating 1W.

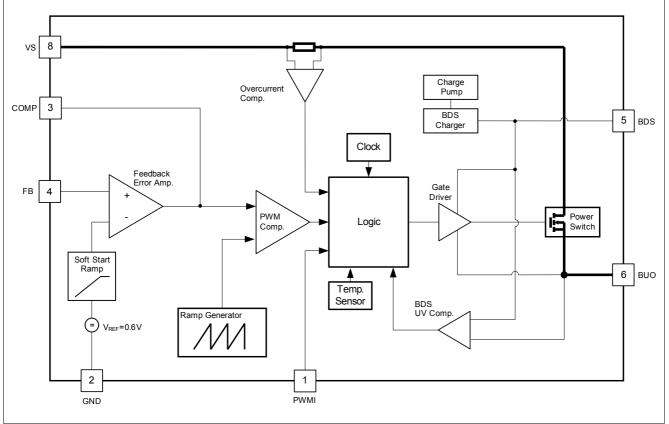

# 5 Buck Regulator

#### 5.1 Description

The gate of the power-switch is driven by the Gate driver which is supplied by the external capacitor connected to pin BDS (Buck Driver Supply) using the bootstrap principle.

BDS is the supply pin for the integrated gate driver of the internal power-switch. The power-switch has to be in the  $R_{DSon}$  region. If  $V_{GS}$  is not high enough, the power-switch can not operate in the  $R_{DSON}$  region, which means high power dissipation. An integrated under voltage lockout function (BDS UV-Comparator) supervising the 'bootstrap' capacitor voltage ensures that the device is always driven with a sufficient bootstrap voltage in order to prevent from extensive heat up of the power-switch.

An integrated charge pump supports the gate driver in case of low input supply voltage, small differential voltage between input supply and output voltage at low current and during startup. In order to minimize emission, the charge pump is switched off if the input voltage is sufficient for supplying the bootstrap.

The soft start function generates a defined ramp of the reference voltage during the first 0.5 ms (typ.) after device initialization and if the Device is autorestarting after a thermal shutdown. This function is disabled during the dimming operation via the PWMI-pin.

Figure 3 Block Diagram Buck Regulator

**Buck Regulator**

#### 5.2 Electrical Characteristics

#### **Electrical Characteristics: Buck Regulator**

$V_{\rm S}$  = 6.0 V to 40 V,  $T_{\rm j}$  = -40 °C to +150 °C, all voltages with respect to ground (unless otherwise specified)

| Pos.   | Parameter                                           | Symbol                        | Li                       | mit Va | lues  | Unit | Conditions                                                                   |  |

|--------|-----------------------------------------------------|-------------------------------|--------------------------|--------|-------|------|------------------------------------------------------------------------------|--|

|        |                                                     |                               | Min.                     | Тур.   | Max.  |      |                                                                              |  |

| 5.2.1  | FB input voltage                                    | V <sub>FB</sub>               | 0.588                    | 0.60   | 0.612 | V    | $V_{\rm EN} = V_{\rm S};$<br>$V_{\rm S} = 12V$<br>$0.1A < I_{\rm CC} < 1.0A$ |  |

| 5.2.2  | -                                                   | V <sub>FB</sub>               | 0.576                    | 0.60   | 0.624 | V    | $V_{\rm EN} = V_{\rm S};$<br>$V_{\rm S} = 12V$<br>1mA < $I_{\rm CC}$ < 1.8A  |  |

| 5.2.3  | FB input current                                    | $I_{FB}$                      | -1                       | -0.1   | 0     | μA   | V <sub>FB</sub> = 0.6V                                                       |  |

| 5.2.4  | Power-Switch on-resistance                          | R <sub>DS(ON)</sub>           | -                        | -      | 500   | mΩ   | $I_{\rm CC}$ =300 mA;<br>$T_{\rm J}$ = 150 °C max.                           |  |

| 5.2.5  | Current transition rise/fall time                   | <i>t</i> <sub>r</sub>         | -                        | 50     | -     | ns   | <i>I</i> <sub>CC</sub> =1 A <sup>1)</sup>                                    |  |

| 5.2.6  | Buck peak over current limit                        | I <sub>BUOC</sub>             | 2.2                      | -      | 3.6   | А    | -                                                                            |  |

| 5.2.7  | Bootstrap under voltage lockout, turn-off threshold | $V_{\rm BDS,off}$             | V <sub>вUO</sub><br>+3.3 | -      | -     | V    | Bootstrap voltage decreasing                                                 |  |

| 5.2.8  | Charge pump current                                 | I <sub>CP</sub>               | 2                        | -      | -     | mA   | $V_{\rm S}$ = 12V;<br>$V_{\rm BUO}$ = $V_{\rm BDS}$ = GND                    |  |

| 5.2.9  | Charge pump switch-off threshold                    | $V_{\rm BDS}$ - $V_{\rm BUO}$ | -                        | -      | 5     | V    | $(V_{\rm BDS}$ - $V_{\rm BUO})$ increasing                                   |  |

| 5.2.10 | Maximum duty cycle                                  | $D_{\max}$                    | -                        | -      | 100   | %    | 1) 2)                                                                        |  |

| 5.2.11 | Soft start ramp                                     | t <sub>start</sub>            | 350                      | 500    | 750   | μs   | $V_{\rm FB}$ rising from 5% to 95% of $V_{\rm FB,nom}$                       |  |

| 5.2.12 | Input under voltage shutdown threshold              | $V_{\mathrm{S,off}}$          | 3.75                     | -      | -     | V    | $V_{\rm S}$ decreasing                                                       |  |

| 5.2.13 | Input voltage startup threshold                     | $V_{\mathrm{S,on}}$           | -                        | -      | 4.75  | V    | $V_{\rm S}$ increasing                                                       |  |

| 5.2.14 | Input under voltage shutdown hysteresis             | $V_{\rm S,hyst}$              | 150                      | -      | -     | mV   | 1)                                                                           |  |

1) Not subject to production test; specified by design.

2) Consider "Chapter 4.2, Functional Range"

# 6 Enable, Thermal Shutdown and PWM Dimming Function

#### 6.1 Description

**Enable Function:** With the enable pin (EN) the device can be set in off-state reducing the current consumption to typ.  $0.1\mu$ A. The enable function features an integrated pull down resistor which ensures that the IC is shut down and the power-switch is off in case the pin EN is not connected.

**Device Wake Up Behavior:** The device initialization is triggered either by the EN voltage level crossing the turnon threshold, rising supply voltage (during EN=H), and also when the device restarts after a thermal shutdown. The softstart ramp starts after the BDS external capacitor is charged.

**Overtemperature Behavior:** The integrated thermal shutdown function turns the power-switch off in case of overtemperature. The typ. junction shutdown temperature is 175°C, with a min. of 150°C. After cooling down the IC will automatically restart operation. The thermal shutdown is an integrated protection function designed to prevent IC destruction when operating under fault conditions. It must not be used for normal operation.

**PWM Dimming Function**: The PWMI signal directly controls the gate driver of the integrated power-switch by overriding the internal control signals.

#### 6.2 Electrical Characteristics Enable, Bias, Thermal Shutdown and PWM Dimming

| Pos.   | Parameter                            | Symbol                 |      | Limit Val | ues  | Unit | Conditions                                                     |  |

|--------|--------------------------------------|------------------------|------|-----------|------|------|----------------------------------------------------------------|--|

|        |                                      |                        | Min. | Тур.      | Max. |      |                                                                |  |

| 6.2.1  | Current Consumption, shut down mode  | $I_{q,OFF}$            | -    | 0.1       | 2    | μA   | $V_{\rm EN}$ = 0.8V;<br>$T_{\rm j}$ < 105°C; $V_{\rm S}$ = 16V |  |

| 6.2.2  | Current Consumption, active mode     | $I_{q,\mathrm{ON}}$    | -    | -         | 7    | mA   | $V_{\rm EN}$ = 5.0V; $I_{\rm CC}$ = 0mA;<br>$V_{\rm S}$ = 16V  |  |

| 6.2.3  | Current Consumption, active mode     | I <sub>q,ON</sub>      | -    | -         | 10   | mA   | $V_{\rm EN}$ = 5.0V; $I_{\rm CC}$ = 1.8A;<br>$V_{\rm S}$ = 16V |  |

| 6.2.4  | Enable high signal valid             | $V_{\mathrm{EN,hi}}$   | 3    | -         | -    | V    | -                                                              |  |

| 6.2.5  | Enable low signal valid              | $V_{\rm EN,lo}$        | -    | -         | 0.8  | V    | -                                                              |  |

| 6.2.6  | Enable hysteresis                    | $V_{\rm EN,HY}$        | 50   | 200       | 400  | mV   | 1)                                                             |  |

| 6.2.7  | Enable high input current            | $I_{\rm EN,hi}$        | -    | -         | 30   | μA   | V <sub>EN</sub> = 16V                                          |  |

| 6.2.8  | Enable low input current             | $I_{\rm EN,lo}$        | -    | 0.1       | 1    | μA   | V <sub>EN</sub> = 0.5V                                         |  |

| 6.2.9  | PWMI high threshold                  | $V_{\rm PWMI,hi}$      | 3    | -         | -    | V    | -                                                              |  |

| 6.2.10 | PWMI low threshold                   | $V_{\rm PWMI,lo}$      | -    | -         | 0.8  | V    | -                                                              |  |

| 6.2.11 | PWMI turn-on delay                   | t <sub>PWM,ON</sub>    | -    | -         | 5    | μs   | 2)                                                             |  |

| 6.2.12 | PWMI turn-off delay                  | t <sub>PWM,OFF</sub>   | -    | -         | 5    | μs   | -                                                              |  |

| 6.2.13 | Over temperature shutdown            | $T_{\rm j,sd}$         | 150  | 175       | 190  | °C   | 1)                                                             |  |

| 6.2.14 | Over temperature shutdown hysteresis | T <sub>j,sd_hyst</sub> | -    | 15        | -    | К    | 1)                                                             |  |

#### Electrical Characteristics: Enable, Bias and Thermal Shutdown

$V_{\rm S}$  = 6.0 V to 40 V,  $T_{\rm i}$  = -40 °C to +150 °C, all voltages with respect to ground (unless otherwise specified)

1) Specified by design. Not subject to production test.

2) At startup current flowing in  $C_{\rm BU1}$ , recommended max. PWM frequency 1kHz@370kHz $f_{\rm sw}$

Oscillator

### 7 Oscillator

#### 7.1 Description

The oscillator turns on the power-switch with a constant frequency while the buck regulating circuit turns the power-switch off in every cycle with an appropriate time gap depending on the output and input voltage.

The internal sawtooth signal used for the PWM generation has an amplitude proportional to the input supply voltage (feedforward).

#### 7.2 Electrical Characteristics Oscillator

#### **Electrical Characteristics: Buck Regulator**

$V_{\rm s}$  = 6.0 V to 40 V,  $T_{\rm i}$  = -40 °C to +150 °C, all voltages with respect to ground (unless otherwise specified)

| Pos.  | Parameter            | Symbol        | Limit Values |      |      | Unit | Conditions |

|-------|----------------------|---------------|--------------|------|------|------|------------|

|       |                      |               | Min.         | Тур. | Max. | -    |            |

| 7.2.1 | Oscillator frequency | $f_{\rm osc}$ | 330          | 370  | 420  | kHz  | -          |

#### **Application Information**

## 8 Application Information

Note: The following information is given as a hint for the implementation of the device only and shall not be regarded as a description or warranty of a certain functionality, condition or quality of the device.

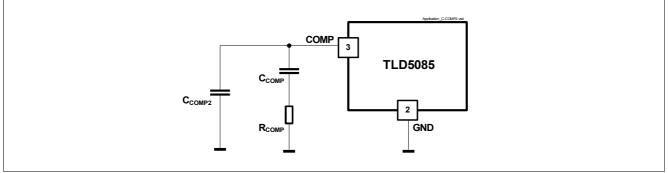

#### 8.1 Frequency Compensation

The stability of the output voltage can be achieved with a simple RC connected between pin COMP and GND. The standard configuration using the switching frequency of the internal oscillator is a ceramic capacitor  $C_{\text{COMP}}$  = 22nF and  $R_{\text{COMP}}$  = 22k $\Omega$ . By slight modifications to the compensation network the stability can be optimized for different types of buck capacitors (ceramic or tantalum).

The compensation network is essential for the control loop stability. Leaving pin COMP open might lead to an instable operation.

#### 8.2 Compensating a tantalum buck capacitor $C_{BU1}$

The TLD5085EJ control loop is optimized for ceramic buck capacitors  $C_{\text{BU}}$ . In order to maintain stability also for tantalum capacitors with ESR up to 300m $\Omega$ , an additional compensation capacitance  $C_{\text{COMP2}}$  at pin COMP to GND is required. It's value calculates:

$$C_{\rm COMP2}$$

=  $C_{\rm BU}$  \*  $ESR(C_{\rm BU})$  /  $R_{\rm COMP}$  ,

whereas  $C_{\text{COMP2}}$  needs to stay below 5nF.

Figure 4 High-ESR buck capacitor compensation

#### 8.3 Freewheeling Diode

In order to minimize losses and for fast recovery, a schottky freewheeling diode is required. Disconnecting the freewheeling diode during operation might lead to destruction of the IC.

#### **Application Information**

#### 8.4 Constant Output Voltage Mode for LED applications

Figure 5 Application Diagram (constant voltage mode)

Note: This is a very simplified example of an application circuit. The function must be verified in the real application

The output voltage of the TLD5085EJ can be programmed by a voltage divider connected to the feedback pin FB. The divider cross current should be 300  $\mu$ A at minimum, therefore the maximum  $R_2$  calculates:

$$R_2 \leq V_{\rm FB}$$

/  $I_{\rm R2}~$  -->  $R_2 \leq$  0.6V / 300  $\mu \rm A$  = 2 k $\Omega$

For the desired output voltage level  $V_{CC}$ ,  $R_1$  calculates then (neglecting the small FB input current):

$$R_1 = R_2 \left( \frac{V_{CC}}{V_{FB}} - 1 \right).$$

#### **Application Information**

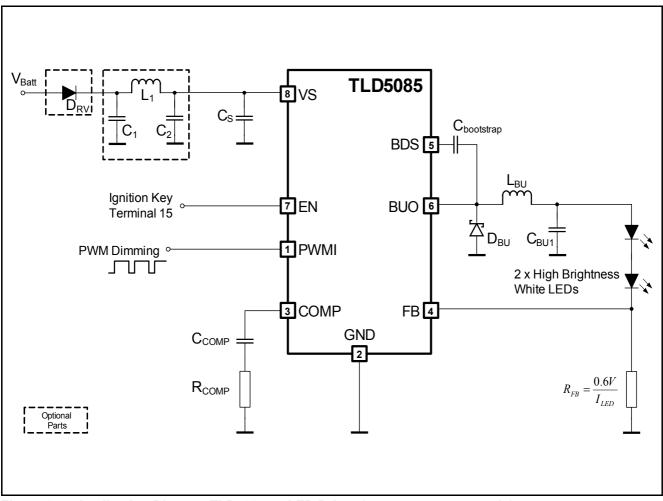

#### 8.5 Constant current mode for LED applications

Figure 6 Application Diagram TLD5085 as LED Driver (constant current mode)

Note: This is a very simplified example of an application circuit. The function must be verified in the real application.

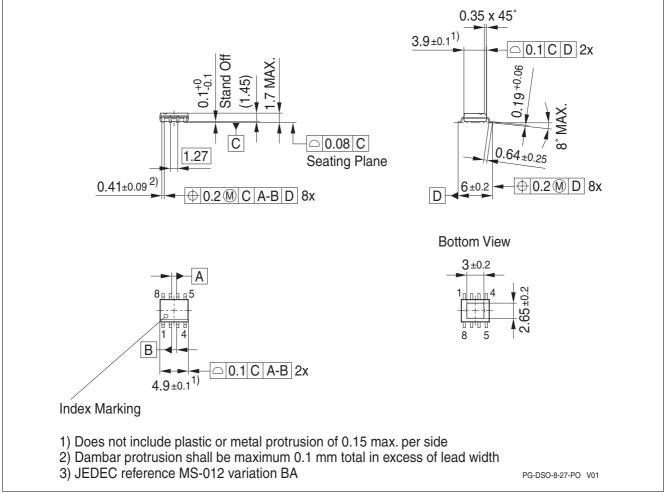

Package Outlines

# 9 Package Outlines

Figure 7 Outline PG-DSO-8 (e-Pad)

#### Green Product (RoHS compliant)

To meet the world-wide customer requirements for environmentally friendly products and to be compliant with government regulations the device is available as a green product. Green products are RoHS-Compliant (i.e Pb-free finish on leads and suitable for Pb-free soldering according to IPC/JEDEC J-STD-020).

For further package information, please visit our website: http://www.infineon.com/packages.

#### **Revision History**

# 10 Revision History

| Version  | Date       | Changes                         |

|----------|------------|---------------------------------|

| Rev. 1.1 | 2009-12-16 | Cover sheet updated             |

|          |            | Package name updated            |

| Rev. 1.0 | 2009-06-04 | Initial Datasheet for TLD5085EJ |

Edition 2009-12-16

Published by Infineon Technologies AG 81726 Munich, Germany © 2009 Infineon Technologies AG All Rights Reserved.

#### Legal Disclaimer

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.